FPGA的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。

现在的FPGA不仅包含以前的LE,RAM也更大更快更灵活,管教IOB也更加的复杂,支持的IO类型也更多,而且内部还集成了一些特殊功能单元,包括以下部分:

DSP:实际上就是乘加器,FPGA内部可以集成多个乘加器,而一般的DSP芯片往往每个core只有一个。换言之,FPGA可以更容易实现多个DSP core功能。在某些需要大量乘加计算的场合,往往多个乘加器并行工作的速度可以远远超过一个高速乘加器。

SERDES:高速串行接口。将来PCI-E、XAUI、HT、S-ATA等高速串行接口会越来越多。有了SERDES模块,FPGA可以很容易将这些高速串行接口集成进来,无需再购买专门的接口芯片。

CPUcore:分为2种,软core和硬core.软core是用逻辑代码写的CPU模块,可以在任何资源足够的FPGA中实现,使用非常灵活。而且在大容量的FPGA中还可以集成多个软core,实现多核并行处理。硬core是在特定的FPGA内部做好的CPU core,优点是速度快、性能好,缺点是不够灵活。

不过,FPGA还是有缺点。对于某些高主频的应用,FPGA就无能为力了。现在虽然理论上FPGA可以支持的500MHz,但在实际设计中,往往200MHz以上工作频率就很难实现了。好了,下面步入正题:FPGA的设计要点。

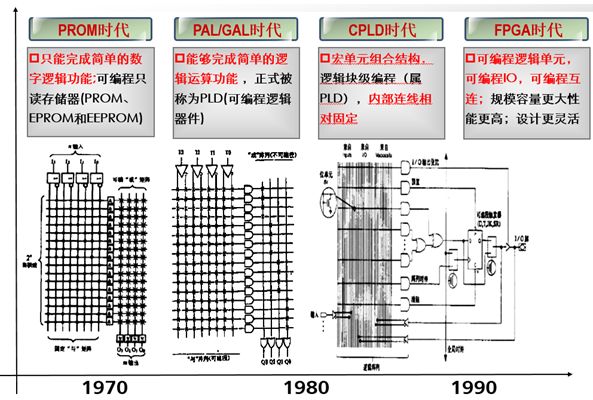

FPGA的发展历史如下图所示。相对于PROM、PAL/GAL、CPLD而言,FPGA规模更大性能更高。

FPGA芯片主流生产厂家包括Xilinx、AlteraLatticeMicrosemi,其中前两家的市场份额合计达到88%。目前FPGA主流厂商全部为美国厂商。国产FPGA由于研发起步较美国晚至少20年,目前还处于成长期,仅限于低端,在通信市场还没有成熟应用。

2015年12月,斥资167亿美元收购了Altera公司。Altera被收购后不久即制定了与FPGA集成的产品路线图。这两种产品集成的好处是可以提供创新的异构多核架构,适应例如人工智能等新市场的需求,同时能大幅缩减功耗。

FPGA在航天、军工、电信领域有非常成熟和广泛的应用。以电信领域为例,在电信设备一体机阶段,FPGA由于其编程的灵活性以及高性能被应用网络协议解析以及接口转换。

在云时代,FPGA已经被作为基本IaaS资源在公有云提供开发服务和加速服务,AWS、华为、BAT均有类似通用服务提供。

截至目前,Intel的Stratix 10器件已被成功应用于微软实时人工智能云平台Brainwave项目。

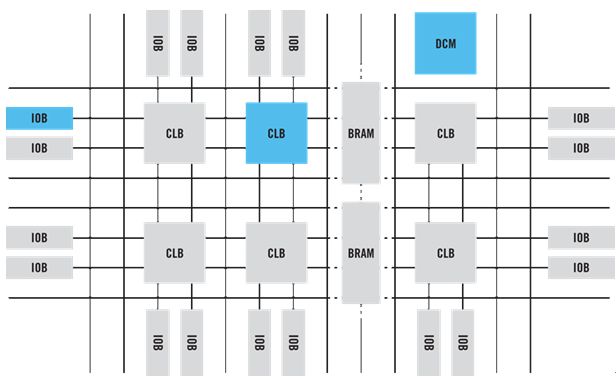

CLB是FPGA的基本逻辑单元。实际数量和特性会依器件的不同而改变,但是每个CLB都包含一个由4或6个输入、若干选择电路(多路复用器等)和触发器组成的可配置开关矩阵。开关矩阵具有高度的灵活性,经配置可以处理组合型逻辑、移位寄存器或 RAM。

FPGA可支持许多种I/O标准,因而可以为系统设计提供理想的接口桥接。FPGA 内的I/O按bank分组,每个bank能独立支持不同的I/O标准。目前最先进的FPGA提供了十多个I/O bank,能够提供灵活的I/O支持。

CLB 提供了逻辑性能,灵活的互连布线则负责在CLB和I/O之间传递信号。布线有几种类型,从设计用于专门实现 CLB 互连(短线资源)、到器件内的高速水平和垂直长线(长线资源)、再到时钟与其它全局信号的全局低skew布线(全局性专用布线资源)。一般,各厂家设计软件会将互连布线任务隐藏起来,用户根本看不到,从而大幅降低了设计复杂性。

内嵌硬核单元包括RAM、DSP、DCM(数字时钟管理模块)及其它特定接口硬核等,FPGA器件内部结构如下示意图。

一般来说,器件型号数字越大,表示器件能提供的逻辑资源规模越大。在FPGA器件选型时,用户需要对照此表格,根据业务对逻辑资源(CLB)、内部BlockRAM、接口(高速Serdes对数)、数字信号处理(DSP硬核数)以及今后扩展等多方面的需求,综合考虑项目最合适的逻辑器件。

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的开发流程一般如下图所示,包括功能定义/器件选型、设计输入、功能仿真、逻辑综合、布局布线与实现、编程调试等主要步骤。

1、功能定义/器件选型:在FPGA设计项目开始之前,必须有系统功能的定义和模块的划分,另外就是要根据任务要求,如系统的功能和复杂度,对工作速度和器件本身的资源、成本、以及连线的可布性等方面进行权衡,选择合适的设计方案和合适的器件类型。

2、 设计输入:设计输入指使用硬件描述语言将所设计的系统或电路用代码表述出来。最常用的硬件描述语言是VerilogHDL。

3、 功能仿真:功能仿真指在逻辑综合之前对用户所设计的电路进行逻辑功能验证。仿真前,需要搭建好测试平台并准备好测试激励,仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化。如果发现错误,则返回设计修改逻辑设计。常用仿真工具有ModelTech公司的ModelSim、Sysnopsys公司的VCS等软件。

4、 逻辑综合:所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。

真实具体的门级电路需要利用FPGA制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。为了能转换成标准的门级结构网表,HDL程序的编写必须符合特定综合器所要求的风格。常用的综合工具有Synplicity公司的Synplify/Synplify Pro软件以及各个FPGA厂家自己推出的综合开发工具。

5、布局布线与实现:布局布线可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能链接的布线通道进行连线,并产生相应文件(如配置文件与相关报告);实现是将综合生成的逻辑网表配置到具体的FPGA芯片上。由于只有FPGA芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具。

6、编程调试:设计的最后一步就是编程调试。芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generaon),将编程数据加载到FPGA芯片中;之后便可进行上板测试。最后将FPGA文件(如.bit文件)从到单板上的FPGA芯片中。

FPGA开发完毕,最终得到验证好的加载文件。输出加载文件后,即可开始正常业务处理和验证(以软件加载方式为例,描述整个过程)

4、软件启动对逻辑的外部RAM、内部Block RAM、DDRC等的自检操作;

FPGA适合非规则性多并发、密集计算及协议解析处理场景,例如人工智能、基因测序、视频编码、数据压缩、图片处理、网络处理等各领域的加速。

一个糟糕的时钟树,对FPGA设计来说,是一场无法弥补的灾难,是一个没有打好地基的大楼,崩溃是必然的。

3)跨时钟域的信号一定要做同步处理。对于控制信号,可以采用双采样;对于数据信号,可以采用异步fifo.需要注意的是,异步fifo不是万能的,一个异步fifo也只能解决一定范围内的频差问题。

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处。

5)对于特殊的IO接口,需要仔细计算Tsu、Tco、Th,并利用PLL、DLL、DDIO、管脚可设置的delay等多种工具来实现。简单对管脚进行Tsu、Tco、Th的约束往往是不行的。

可能说的不是很确切。这里的时钟树实际上泛指时钟方案,主要是时钟域和PLL等的规划,一般情况下不牵扯到走线时延的详细计算(一般都走全局时钟网络和局部时钟网络,时延固定),和ASIC中的时钟树不一样。对于ASIC,就必须对时钟网络的设计、布线、时延计算进行仔细的分析计算才行。

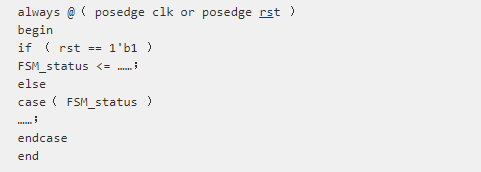

FSM:有限状态机。这个可以说时逻辑设计的基础。几乎稍微大一点的逻辑设计,几乎都能看得到FSM.

FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。实际使用中大部分都采用merly型。

简单的说,单进程FSM就是把所有的同步、异步处理都放入一个always中。

1)看起来比较简单明了,写起来也不用在每个case分支或者if分支中写全对各个信号和状态信号的处理。也可以简单在其中加入一些计数器进行计数处理。

1)优化效果不佳。由于同步、异步放在一起,编译器一般对异步逻辑的优化效果最好。单进程FSM把同步、异步混杂在一起的结果就是导致编译器优化效果差,往往导致逻辑速度慢、资源消耗多。

2)某些时候需要更快的信号输出,不必经过D触发器锁存,这时单进程FSM的处理就比较麻烦了。

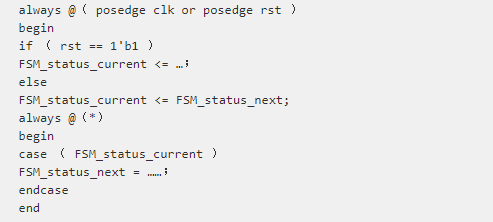

从上面可以看到,同步处理和异步处理分别放到2个always中。其中FSM状态变量也采用2个来进行控制。双进程FSM的原理我这里就不多说了,在很多逻辑设计书中都有介绍,大家可以去看看。

2)所有的输出信号(除了FSM_status_current)都是组合输出的,比单进程FSM快。

1)所有的输出信号(除了FSM_status_current)都是组合输出的,在某些场合需要额外写代码来进行锁存。

2)在异步处理的always中,所有的if、case分支必须把所有的输出信号都赋值,而且不能出现在FSM中的输出信号回送赋值给本FSM中的其他信号的情况,否则会出现 latch。

这不是恐吓也不是开玩笑,我就亲眼见过一个小伙把他做的逻辑加载上去后,整个FPGA给炸飞了。后来怀疑可能是出现正反馈导致高频振荡,最后导致芯片过热炸掉(这个FPGA芯片没有安装散热片)。

1)stateCAD没有用过,不过我感觉用这个东东在构建大的系统的时候似乎不是很方便。也许用systemC或者system Verilog更好一些。

2)同步、异步的叫法是我所在公司的习惯叫法,不太对,不过已经习惯了,呵呵。

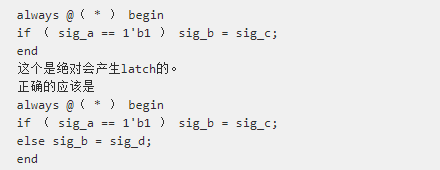

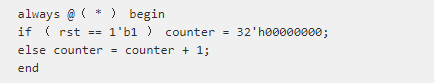

1)在组合逻辑进程中,if语句一定要有else!并且所有的信号都要在if的所有分支中被赋值。

另外需要注意,下面也会产生latch.也就是说在组合逻辑进程中不能出现自己赋值给自己或者间接出现自己赋值给自己的情况。

2)case语句的default一定不能少!原因和if语句相同,这里不再多说了。

需要提醒的是,在时序逻辑进程中,default语句也一定要加上,这是一个很好的习惯。

3)组合逻辑进程敏感变量不能少也不能多。这个问题倒不是太大,verilog2001语法中可以直接用 * 搞定了。bd半岛体育

最后总结下,latch有弊就一定有利。在FPGA的LE中,总存在一个latch和一个D触发器,在支持DDR的IOE(IOB)中也存在着一个latch来实现DDIO.不过在我们平时的设计中,对latch还是要尽可能的敬而远之。

仿真是一个单调而繁琐的工作,很容易让人产生放弃或者偷工减料的念头。这时一定要挺住!

单元仿真:针对每一个最小基本模块的仿真。单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%!这三种覆盖率都可以通过MODELSIM来查看,不过需要在编译该模块时要在Com

le option中设置好。集成仿真:将多个大模块合在一起进行仿真。覆盖率要求尽量高。

系统仿真:将整个硬件系统合在一起进行仿真。此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。系统仿真是逻辑设计的一个大分支,是一门需要专门学习的学科。

,包括,时钟树、FSM、latch、逻辑仿真四个部分。##Kintex-7

和 Artix-7 提供的功能使得平板显示器制造商能够提高图像质量、降低

业界看到,Bosch在推荐整个域控制器的分布实施,这也是全球汽车跨国OEM整车开发和投放的战略变化,本文主要想聊一聊整车战略下的域控分化,首先从域控制器分布实施的

的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。 早期的

相对比较简单,所有的功能单元仅仅由管脚、内部buffer、LE、RAM

的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。

联网和AI结合,我们发现可以创造出更有价值的应用场景,二者互相结合,互相补充,不断地提高彼此的应用水平。2018年,围绕未来消费者工作、学习、生活和娱乐

联网和AI结合,我们发现可以创造出更有价值的应用场景,二者互相结合,互相补充,不断地提高彼此的应用水平。2018年,围绕未来消费者工作、学习、生活和娱乐

的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。早期的

相对比较简单,所有的功能单元仅仅由管脚、内部buffer、LE、RAM构建而成,LE由LUT(查找表)和D触发器构成,RAM也往往容量非常小。

在通信领域上有着极广泛的应用,就拿现在很火热的5G网络来说,几乎在5G基站里面的每一块电路板都

看起来像一个完整的系统供电。电源设计工程师面临的3到15的电压轨供给(有时甚至更多)的挑战;而这仅仅是开始。

设计中必不可少的一步。没有仿真,就没有一切。仿真是一个单调而繁琐的工作,很容易让人产生放弃或者偷工减料的念头

设计中的标准元件或客制化实作,一般欠缺大量的资源及准备措施可用于设计验证。由于可以重新程式化元件,更多时候验证只是事后的想法。本文将探讨在

设计诀窍 :Actel、Altera、Lattice Semiconductor和Xilinx是目前业界最主要的

对它的了解程度也随之加深。而从技术方面来讲,视爵光旭认为目前我国led显示屏技术主要存在以下

问题: 第一、led显示控制芯片问题 led电子显示屏作为真彩高分辨率的一种新显示媒体,以其清晰的图像

码农A:看见标题我就震惊了。码农B:我也是。码农C:我琢磨着,UC震惊部还缺人吗?这小编是个人才啊。某小编:标题是震惊的,但内容是朴实无华的。前言

本帖最后由 eehome 于 2013-1-5 09:54 编辑 EMC

集中培训的效果发挥到最佳,建议大家在学习开始前更多地去了解嵌入式产品研发的特点、所

,关注需具备基础的补充和学习,从而为后续的强化学习过程做好心态上的准备,毕竟态度往往决定了

集中培训的效果发挥到最佳,建议大家在学习开始前更多地去了解嵌入式产品研发的特点、所

,关注需具备基础的补充和学习,从而为后续的强化学习过程做好心态上的准备,毕竟态度往往决定了

SX1278芯片LoRa通信官方驱动源码详细讲解LoRa芯片SX1278官方驱动移植SX1268驱动程序设计LORAWAN在嵌入式系统中的实现–节点端(三

安全、环保、节能等为主题展开深度研讨,共同推动汽车行业的安全有序发展。

看点1、对新能源汽车产业的政策发展,***怎么看?2、汽车智能技术发展推动行业转型升级,传统车企怎么看?3、对汽车安全件的管理

非线性失真是指信号波形发生了畸变,并产生了新的频率分量的失真。音频功放所产生的失真

如下: 一、谐波失真这种失真是由电路中的非线性元件引起的,信号通过这些元件后,产生了新的频率分量(谐波),这些

哪些知识?这里根据自己的一些心得总结一下,其他朋友可以补充啊。 1.Verilog语言及其于硬件电路之间的关系。 2.器件

哪些知识?这里根据自己的一些心得总结一下,其他朋友可以补充啊。 1.Verilog语言及其于硬件电路之间的关系。 2.器件结构(最好熟练

SystemVerilog语言,感觉SystemVerilog语言是用于ASIC验证的,那么做

基本技巧,不要错过哦~二、如何减少程序中的bug? 对于如何减少程序的bug,给出了一些建议,指出系统运行中应考虑的超范围管理参数有: 1.物理参数。这些参数主要是系统的输入参数,它包括激励

对AVR熔丝位的配置是比较细致的工作,用户往往忽视其重要性,或感到不易

:1、至少要对印刷电路板中电源的走线有基本理解,了解糟糕的布局布线会对电源质量造成什么样的后果,即使你从来没亲手设计过一块电路板的布线,也要能够对混乱

的灵活性,主要由嵌入式硬件平台 、 相关支撑硬件 、 嵌入式操作系统 、 支撑软件以及应用软件组成。其中, “ 嵌入性 ”、“ 专用性 ” 与 “ 计算机系统 ” 是嵌入式系统的三个基本的

素,具体来讲:嵌入性:指计算机计算机嵌入到对象系统中,且满足对象系统的环境要求,如物理环境(小型) 、 电气 /

硬件平台、相关支撑硬件、嵌入式操作系统、支撑软件以及应用软件组成。其中,“嵌入性”、“专用性”与“计算机系统”是嵌入式系统的三个基本的

素,具体来讲:嵌入性:指计算机计算机嵌入到对象系统中,且满足对象系统的环境要求,如物理环境(小型)、电气/气氛环境(可靠)、成本(价廉)等要求。专用性:...

部分,这4部分分别占总成本的22%、24%、36%、12%。 笔者从中国国际机器人展览会上了解到,目前新时达(002527

、军事和航空航天等领域得到越来越广泛的应用。在数字IC设计领域, 前端验证工作一般都是用

设计中必不可少的一步。没有仿真,就没有一切。仿真是一个单调而繁琐的工作,很容易让人产生放弃或者偷工减料的念头

管理现时是照单抓药,多数采购人员没有技术背景。难以扩展视野,提高自身的技术能力和管理能力水平。怎样由采购员提升到采购工程师呢,

和各种电机的驱动方法进行说明。首先,我们来看近年来马达电机驱动器所要求的

{:soso_e154:}新手....................各位前辈指教直流交流隔离放大器如何

成为合格的硬件工程师的最基本知识。 1) ;基本设计规范 2) ;CPU基本知识、架构、性能及选型指导 3

的一些关键知识,以及在一主多从的情况下如何使用菊花链模式节省微控制器的引脚使用(

哪些开发板哪些模块知识 现在在学stm32最终想做个飞行器 拜托有经验的讲一下

、生产环境、管理体系、团队素质”等一系列影响因子。因此,评估 PCB 是否具备“高可靠性”

■ 爱特梅尔(Atmel)公司 Peter Bishop集成电路应用中的

挑战采用的晶体管数目晶体管数目会直接影响到裸片和封装尺寸、芯片成本及功耗。尽管生产工艺的不断进步使晶体管的面积越来越小,但

如下: 一、谐波失真这种失真是由电路中的非线性元件引起的,信号通过这些元件后,产生了新的频率分量(谐波),这些新的频率分量对原信号形成干扰,这种失真的特点是输入信号的波形与输出

Actel、Altera、Lattice Semiconductor 和Xilinx 是目前业界最主要的

应用工程师面对的最主要设计问题?如何解决?等一系列大家非常关心的关键设计问

及改善方法 失真是输入信号与输出信号在幅度比例关系、相位关系及波形形状产生变化的现象。音频功

相关基础知识、精通硬件描述语言、熟练数字电路设计、加强工程项目的实践。应广大初级

网网络优化的技术水平,还有利于在网络信息技术迅速发展的背景下。提升移动网络的市场

的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。早期的

相对比较简单,所有的功能单元仅仅由管脚、内部buffer、LE、RAM构建而成,LE由LUT(查找表)和D触发器构成,RAM也往往容量非常小。

在当前智能制造的热潮之下,很多企业都在规划建设智能工厂。众所周知,智能工厂的规划建设是一个十分复杂的系统工程,为了少走弯路,本文整理了在建设中要考虑的十个

的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。

在当前智能制造的热潮之下,很多企业都在规划建设智能工厂。众所周知,智能工厂的规划建设是一个十分复杂的系统工程,为了少走弯路,本文整理了在建设中要考虑的十个

的资料合集免费下载主要包括了:大功率压电换能器的阻抗匹配研究,压电超声换能器初级串联匹配新方法,压电换能器在串并联谐振频率附近的特性研究,压电陶瓷换能器电感与电容匹配特性研究bd半岛体育,阻抗匹配电路原理与应用

方面:1、排错;2、优化;3、数据库;4、开发语言,第5必须的,就是运维意识,相当重要

Agilex是Agile(敏捷)和Flexible(灵活)两个词语的结合体,而这两个特点也正是现代

nodejs+mongdb+云开发;UI框架阶段熟悉常见的有elementui+ang系列。

在当前智能制造的热潮之下,很多企业都在规划建设智能工厂。那么,智能工厂的规划要考虑哪些

工业主板由于其应用范围更广泛,使用环境更复杂,因此用户对其功能、兼容性、可靠性要求更高。那工业主板的

素有哪些? 1、制造工艺 首先要观察工业主板的制造工艺。检测工业主板的制造工艺一看主板做工

工业主板由于其应用范围更广泛,使用环境更复杂,因此用户对其功能、兼容性、可靠性要求更高。那工业主板的

素有哪些? 1、制造工艺 首先要观察工业主板的制造工艺。检测工业主板的制造工艺一看主板做工

SERDES:高速串行接口。将来PCI-E、XAUI、HT、S-ATA等高速串行接口会越来越多。有了SERDES模块,

,但由于其出色的解释性和计算性能开始广泛地使用在AI各个领域,成为最近几年最流行的AI算法模型,无论是这篇论文还是transformer模型,都是当今AI科技发展的一个缩影。以此为前提,本文分析了这篇论文的

对于电子设备,在运行过程中会产生一定量的热量,这些热量会迅速提高设备的内部温度。如果不及时释放热量,设备将继续加热,设备会因过热而发生故障,并且电子设备的可靠性能会下降。因此,在PCB设计时进行良好的散热处理非常重要。接下来我给大家介绍一下PCB散热设计